D

С

Α

7 6 5

CST-Kavlico Confidential Proprietary:

Property of CST-Kavlico. Not to be reproduced by any means or used to furnish information to others without explicit written consent of CST-Kavlico. All rights reserved.

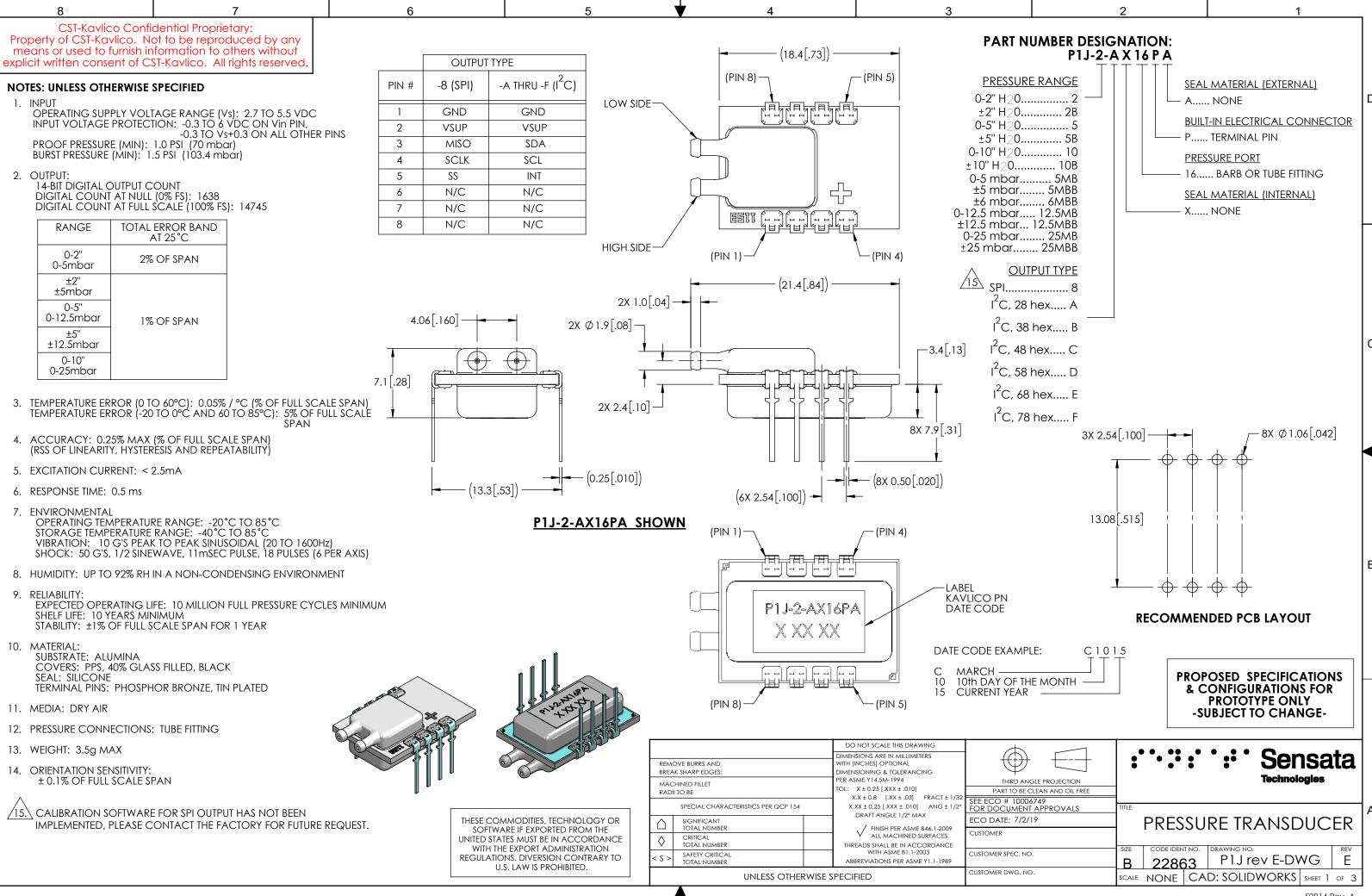

# 1<sup>2</sup>C COMMUNICATION

### 1<sup>2</sup>C INTERFACE:

D

С

В

| OUTPUT                       |                                                           |                            |                       |      |                       |       |  |

|------------------------------|-----------------------------------------------------------|----------------------------|-----------------------|------|-----------------------|-------|--|

| RESOLUTION                   | 12 Bits MINIMUM (11BITS MINIMUM FOR 0-2" AND 0-5mb RANGE) |                            |                       |      |                       |       |  |

| UPDATE RATE                  | 0.5 ms                                                    | 0.5 ms                     |                       |      |                       |       |  |

| VOLTAGE                      | SYMBOL                                                    | CONDITIONS                 | MIN                   | TYP  | MAX                   | UNITS |  |

| HIGH-LEVEL INPUT VOLTAGE     | V <sub>IH</sub>                                           | -                          | 0.8 X V <sub>DD</sub> | -    | V <sub>DD</sub>       | ٧     |  |

| LOW-LEVEL INPUT VOLTAGE      | V <sub>IL</sub>                                           | -                          | -                     | -    | 0.2 X V <sub>DD</sub> | ٧     |  |

| HIGH-LEVEL OUTPUT VOLTAGE    | V <sub>OH</sub>                                           | -                          | V <sub>DD</sub> -0.2  | -    | V <sub>DD</sub>       | ٧     |  |

| LOW-LEVEL OUTPUT VOLTAGE     | V <sub>OL</sub>                                           | -                          | 0                     | -    | 0.2                   | ٧     |  |

| PARAMETER                    |                                                           |                            |                       |      |                       |       |  |

| OUTPUT SOURCING CURRENT      | I <sub>OH_SDA</sub>                                       | SDA @V <sub>OH</sub> , MIN | -1.9                  | -3.1 | -4.8                  | mA    |  |

|                              | I <sub>OH_INT</sub>                                       | INT @V <sub>OH</sub> , MIN | -0.63                 | -1.2 | -1.9                  | mA    |  |

| OUTPUT SINK CURRENT          | I <sub>OL_SDA</sub>                                       | SDA @V <sub>OL</sub> , MAX | 2.3                   | 3.9  | 6.2                   | mA    |  |

|                              | I <sub>OL_INT</sub>                                       | INT @V <sub>OL</sub> , MAX | 0.85                  | 1.7  | 3.0                   | mA    |  |

| LOAD CAPACITANCE AT SDA      | C <sub>SDA</sub>                                          | @ 400kHz                   | -                     | -    | 200                   | рF    |  |

| PULL-UP RESISTOR             | R <sub>I2C_PU</sub>                                       | -                          | 0.5                   | 1    | 50                    | kΩ    |  |

| INPUT CAPACITANCE (EACH PIN) | C <sub>I2C_IN</sub>                                       | -                          | -                     | -    | 10                    | pF    |  |

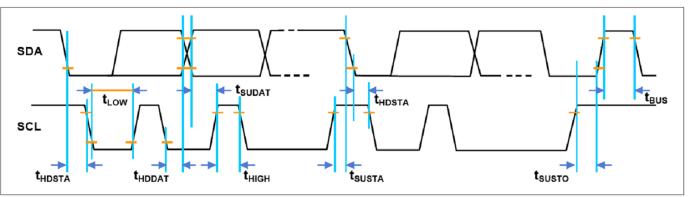

#### TIMING:

| PARAMETER                                                              |                    | MIN | TYP | MAX | UNITS |  |

|------------------------------------------------------------------------|--------------------|-----|-----|-----|-------|--|

| SCL clock frequency                                                    |                    | 100 |     | 400 | kHz   |  |

| Start condition hold time relative to SCL edge                         | t <sub>HDSTA</sub> | 0.1 |     |     | μs    |  |

| Minimum SCL clock low width 1)                                         | t <sub>LOW</sub>   | 0.6 |     |     | μs    |  |

| Minimum SCL clock high width 1)                                        | t <sub>HIGH</sub>  | 0.6 |     |     | μs    |  |

| Start condition setup time relative to SCL edge                        |                    | 0.1 |     |     | μs    |  |

| Data hold time on SDA relative to SCL edge                             | t <sub>HDDAT</sub> | 0   |     |     | μs    |  |

| Data setup time on SDA relative to SCL edge                            | t <sub>SUDAT</sub> | 0.1 |     |     | μs    |  |

| Stop condition setup time on SCL                                       | t <sub>susto</sub> | 0.1 |     |     | μs    |  |

| Bus free time between stop condition and start condition               | t <sub>BUS</sub>   | 2   |     |     | μs    |  |

| Combined low and high widths must equal or exceed minimum SCLK period. |                    |     |     |     |       |  |

#### TIMING DIAGRAM:

NOTE: THERE ARE THREE ADJUSTMENTS TO THE 1<sup>2</sup>C IMPLEMENTATION COMPARED WITH THE ORIGINAL 1<sup>2</sup>C PROTOCOL:

- Sending a start-stop condition without any transitions on the CLK line (no clock pulses in between) creates

a communication error for the next communication, even if the next start condition is correct and the clock

pulse is applied. An additional start condition must be sent, which results in restoration of proper

communication.

- The restart condition—a falling SDA edge during data transmission when the CLK clock line is still high—creates the same situation. The next communication fails, and an additional start condition must be sent for correct communication.

- A falling SDA edge is not allowed between the start condition and the first rising SCL edge. If using an I<sup>2</sup>C™ address with the first bit 0, SDA must be held low from the start condition through the first bit.

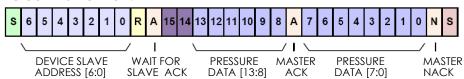

## 1<sup>2</sup>C COMMUNICATION:

#### **DIAGNOSTIC FEATURES:**

THE P1J OFFERS A FULL SUITE OF DIAGNOSTIC FEATURES TO ENSURE ROBUST SYSTEM OPERATION. THE DIAGNOSTIC STATES ARE INDICATED BY A TRANSMISSION OF THE STATUS OF THE 2 MSBs OF THE BRIDGE HIGH BYTE DATA OR BY A SATURATED OUTPUT AT 3FFF...

| ***                                       |                                                                                                                                                                                                                                                                                                        |

|-------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| STATUS BITS<br>(2 MSBs OF OUTPUT PACKAGE) | DEFINITION                                                                                                                                                                                                                                                                                             |

| 00                                        | NORMAL OPERATION, GOOD DATA PACKET                                                                                                                                                                                                                                                                     |

| 01                                        | RESERVED (WILL NOT BE SEEN DURING OPERATION)                                                                                                                                                                                                                                                           |

| 10                                        | STALE DATA: DATA THAT HAS ALREADY BEEN FETCHED SINCE THE LAST MEASUREMENT CYCLE. NOTE: IF A DATA FETCH IS PERFORMED BEFORE OR DURING THE FIRST MEASUREMENT AFTER POWER-ON RESET, THEN "STALE" WILL BE RETURNED, BUT THIS DATA IS ACTUALLY INVALID BECAUSE THE FIRST MEASUREMENT HAS NOT BEEN COMPLETED |

| 11                                        | DIAGNOSTIC CONDITION EXISTS                                                                                                                                                                                                                                                                            |

s Start Condition

Device Slave Address (example: Bit 5)

Data Bit (example: Bit 2)

Read/Write Bit (example: Read=1)

A Acknowledge (ACK)

No Acknowledge (NACK)

S Stop Condition

Status Bit

THESE COMMODITIES, TECHNOLOGY OR SOFTWARE IF EXPORTED FROM THE UNITED STATES MUST BE IN ACCORDANCE WITH THE EXPORT ADMINISTRATION REGULATIONS. DIVERSION CONTRARY TO U.S. LAW IS PROHIBITED.

SIZE CODE IDENT NO. B 22863 P1J-DWG E

SCALE NONE CAD: SOLIDWORKS SHEET 2 OF 3

6

5

**15** SPI COMMUNICATION

2

CST-Kavlico Confidential Proprietary:

Property of CST-Kavlico. Not to be reproduced by any

means or used to furnish information to others without

explicit written consent of CST-Kavlico. All rights reserved.

SPI READINGS WILL BE PROVIDED IN A DUPLEX 3-WIRE READ ONLY FORMAT. THE ENTIRE OUTPUT PACKET CONSISTS OF 4 BYTES (32 bits). THE HIGH BYTE OF THE PRESSURE DATA IS TRANSMITTED FIRST, FOLLOWED BY THE LOW BYTE. THEN 14 bits OF OPTIONAL TEMPERATURE DATA [(TC13:0]) ARE SENT. THE LAST 2 bits OF THE FINAL BYTE ARE "DO NOT CARE" AND SHOULD BE IGNORED. IF THE OPTIONAL TEMPERATURE DATA IS REQUIRED, PLEASE CONTACT THE KAVLICO SALES TEAM. FOR ALL OTHER APPLICATIONS, THE READ CAN BE TERMINATED AFTER THE 2ND BYTE.

#### **SPI INTERFACE:**

D

С

В

Α

| OUTPUT                       |                      |                              |                       |        |                       |       |

|------------------------------|----------------------|------------------------------|-----------------------|--------|-----------------------|-------|

| RESOLUTION                   | 12 Bits N            | IINUMUM (11 BITS MINIMUM FOI | R 0-2" AND 0-5m       | b RANC | ЭЕ)                   |       |

| UPDATE RATE                  | 0.5 ms               |                              |                       |        |                       |       |

| VOLTAGE                      | SYMBOL               | CONDITIONS                   | MIN                   | TYP    | MAX                   | UNITS |

| HIGH-LEVEL INPUT VOLTAGE     | V <sub>IH</sub>      | -                            | 0.8 X V <sub>DD</sub> | -      | V <sub>DD</sub>       | ٧     |

| LOW-LEVEL INPUT VOLTAGE      | V <sub>IL</sub>      | -                            | -                     | -      | 0.2 X V <sub>DD</sub> | ٧     |

| HIGH-LEVEL OUTPUT VOLTAGE    | V <sub>OH</sub>      | -                            | V <sub>DD</sub> -0.2  | -      | V <sub>DD</sub>       | ٧     |

| LOW-LEVEL OUTPUT VOLTAGE     | V <sub>OL</sub>      | -                            | 0                     | -      | 0.2                   | ٧     |

| PARAMETER                    |                      |                              |                       |        |                       |       |

| OUTPUT SOURCING CURRENT      | I <sub>OH_MISO</sub> | MISO @V <sub>OH</sub> , MIN  | -1.9                  | -3.1   | -4.8                  | mA    |

|                              | I <sub>OH_SS</sub>   | SS @V <sub>OH</sub> , MIN    | -0.63                 | -1.2   | -1.9                  | mA    |

| OUTPUT SINK CURRENT          | I <sub>OL_MISO</sub> | MISO @V <sub>OL</sub> , MAX  | 2.3                   | 3.9    | 6.2                   | mA    |

|                              | I <sub>OL_SS</sub>   | SS @V <sub>OL</sub> , MAX    | 0.85                  | 1.7    | 3.0                   | mA    |

| INPUT CAPACITANCE (EACH PIN) | C <sub>I2C_IN</sub>  | -                            | -                     | -      | 10                    | рF    |

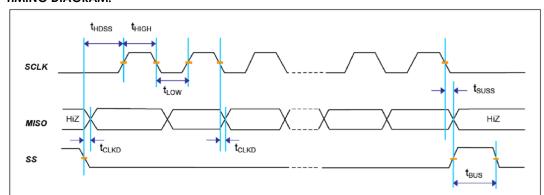

#### TIMING:

| PARAMETER                                                              | SYMBOL            | MIN | TYP | MAX | UNITS      |  |

|------------------------------------------------------------------------|-------------------|-----|-----|-----|------------|--|

| SCLK clock frequency                                                   |                   | 50  |     | 800 | kHz        |  |

| SS drop to first clock edge                                            | t <sub>HDSS</sub> | 2.5 |     |     | μ <b>s</b> |  |

| Minimum SCLK clock low width 1)                                        | t <sub>LOW</sub>  | 0.6 |     |     | μ <b>s</b> |  |

| Minimum SCLK clock high width 1)                                       | t <sub>HIGH</sub> | 0.6 |     |     | μ <b>s</b> |  |

| Clock edge to data transition                                          | t <sub>CLKD</sub> | 0   |     | 0.5 | μ <b>s</b> |  |

| Rise of SS relative to last clock edge                                 | t <sub>SUSS</sub> | 0.1 |     |     | μ <b>s</b> |  |

| Bus free time between rise and fall of SS                              | t <sub>BUS</sub>  | 2   |     |     | μ <b>s</b> |  |

| Combined low and high widths must equal or exceed minimum SCLK period. |                   |     |     |     |            |  |

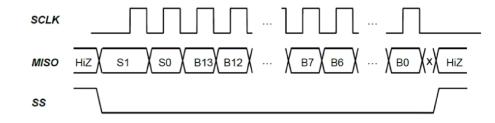

#### TIMING DIAGRAM:

NOTE: THE MISO LINE IS SETUP TO CHANGE STATE ON THE FALLING EDGE OF THE SCLK CLOCK. ACCORDINGLY, THE MASTER SHOULD SAMPLE THE DATA ON THE RISING EDGE OF THE SCLK SIGNAL.

#### **OUTPUT PACKET WITH POSITIVE EDGE SAMPLING:**

PACKET = [ {\$(1:0), B(13:8)}, { B(7:0)}] WHERE

\$(1:0) = STATUS bits OF PACKET (NORMAL, STALE DIAGNOSTIC)

B(13:8) = UPPER 6 bits OF 14-bit PRESSURE DATA

B(7:0) = LOWER 8 bits OF 14-bit PRESSURE DATA

HIZ = HIGH IMPEDANCE

#### **DIAGNOSTIC FEATURES:**

THE P1J OFFERS A FULL SUITE OF DIAGNOSTIC FEATURES TO ENSURE ROBUST SYSTEM OPERATION. THE DIAGNOSTIC STATES ARE INDICATED BY A TRANSMISSION OF THE STATUS OF THE 2 MSBs OF THE BRIDGE HIGH BYTE DATA OR BY A SATURATED OUTPUT AT 3FFF...

| STATUS BITS<br>(2 MSBs OF OUTPUT PACKAGE) | DEFINITION                                                                                                                                                                                                                                                                                              |

|-------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 00                                        | NORMAL OPERATION, GOOD DATA PACKET                                                                                                                                                                                                                                                                      |

| 01                                        | RESERVED (WILL NOT BE SEEN DURING OPERATION)                                                                                                                                                                                                                                                            |

| 10                                        | STALE DATA: DATA THAT HAS ALREADY BEEN FETCHED SINCE THE LAST MEASUREMENT CYCLE.  NOTE: IF A DATA FETCH IS PERFORMED BEFORE OR DURING THE FIRST MEASUREMENT AFTER POWER-ON RESET, THEN "STALE" WILL BE RETURNED, BUT THIS DATA IS ACTUALLY INVALID BECAUSE THE FIRST MEASUREMENT HAS NOT BEEN COMPLETED |

| 11                                        | DIAGNOSTIC CONDITION EXISTS                                                                                                                                                                                                                                                                             |

THESE COMMODITIES, TECHNOLOGY OR SOFTWARE IF EXPORTED FROM THE UNITED STATES MUST BE IN ACCORDANCE WITH THE EXPORT ADMINISTRATION REGULATIONS. DIVERSION CONTRARY TO U.S. LAW IS PROHIBITED.

| B     | 22863 |     | P1J-DWG       |       |   | RE | V<br> |

|-------|-------|-----|---------------|-------|---|----|-------|

| SCALE | NONE  | CAE | D: SOLIDWORKS | SHEET | 3 | OF | 3     |